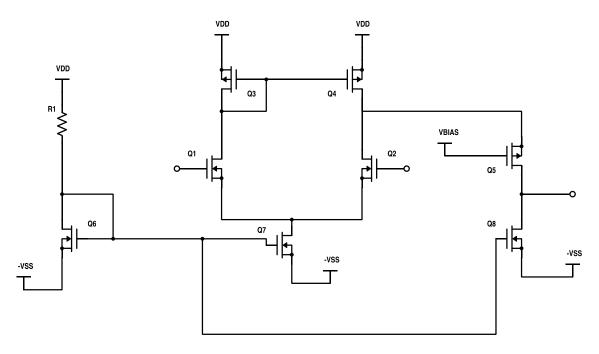

The circuit shown below is a differential amplifier. The transistors Q1, Q2, Q6, Q7, and Q8 are NMOS. Q3, Q4, and Q5 are PMOS. All transistors have their bodies connected to their sources, as shown in the figure. The non-inverting input is located at the gate of Q1, inverting input is located at the gate of Q2, and the output is located at the connected drains of Q5 and Q6.

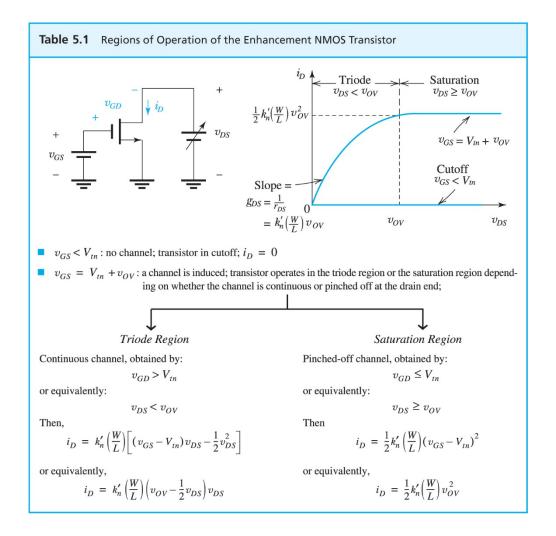

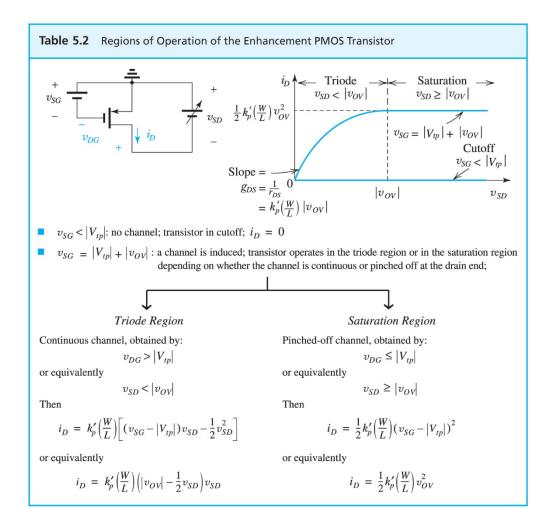

The parameters have the following values (see the attached tables 5.1, 5.2, and 7.2):  $V_{tn}=|V_{tp}|=0.5V$ ,  $k_n'=2k_p'=40\mu A/V^2$ ,  $|V_A|=10V$ .

## W/L ratios:

| <u>Q1</u> | Q2   | Q3        | Q4   | <u>Q5</u> |

|-----------|------|-----------|------|-----------|

| 20/1      | 20/1 | 40/1      | 80/1 | 40/1      |

| <u>Q6</u> | Q7   | <u>Q8</u> |      |           |

| 20/1      | 40/1 | 20/1      |      |           |

Finally  $V_{DD}$ =- $V_{SS}$ =5V and the resistor R1 has been selected to make the drain current of Q6 equal to  $9\mu$ A. VBIAS is adjusted to allow for maximum output range.

- a) Determine the overall differential voltage gain of this amplifier. (2 points)

- b) What value of VBIAS gives the maximum output range? What is that range? (1 point)

- c) The voltage gain of this amplifier can be boosted significantly if Q8 is modified by adding an identical transistor in a cascode connection to Q8 (call it Q8A). If this is done what will the gain increase? (1 point)

Small-Signal Parameters

## **NMOS** transistors

**■** Transconductance:

$$g_m = \mu_n C_{ox} \frac{W}{L} V_{OV} = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D} = \frac{2I_D}{V_{OV}}$$

Output resistance:

$$r_o = V_A/I_D = 1/\lambda I_D$$

## **PMOS** transistors

Same formulas as for NMOS except using  $|V_{OV}|$ ,  $|V_A|$ ,  $|\lambda|$  and replacing  $\mu_n$  with  $\mu_p$ .

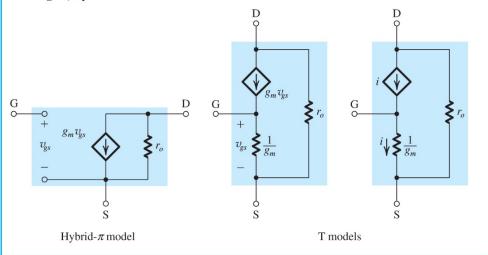

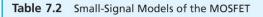

## Small-Signal, Equivalent-Circuit Models